En octobre dernier, NXP avait dévoilé sous le nom de S32 une plate-forme générique à la fois matérielle et logicielle qui vise à unifier l’architecture de traitement de ses microcontrôleurs et microprocesseurs pour l’automobile et à fournir un environnement logiciel identique pour différentes applications au sein d’un véhicule. ...Le fournisseur de semi-conducteurs, toujours en passe d’être racheté par Qualcomm, annonce aujourd’hui les premiers microprocesseurs compatibles avec cette plate-forme. Référencées S32S, ces puces-systèmes, dont l’échantillonnage est prévu à partir du quatrième trimestre 2018, sont conçues pour gérer des fonctions qui nécessitent hautes performances et sûreté de fonctionnement (direction, accélération, freinage…) dans les prochaines générations de véhicules électriques et/ou autonomes.

Selon NXP, les processeurs S32S, gravés en technologie 16 nm, sont les premiers à tirer profit des cœurs Arm Cortex-R52 dans le cadre d’un environnement multicœur conforme aux exigences du niveau Asil D, le niveau de sûreté de fonctionnement le plus élevé stipulé par la norme automobile ISO 26262. Pour rappel, le Cortex-R52 est le premier cœur de processeur temps réel lancé par le britannique Arm qui implémente l’architecture ARMv8-R, dévoilée en 2013 (lire notre article ici). Cette architecture pour processeurs embarqués temps réel est justement destinée à satisfaire les contraintes de sûreté de fonctionnement typiquement rencontrées sur les marchés de l’automobile et de l’industriel. Bâtie sur les fondamentaux de l’architecture 32 bits ARMv7-R, aujourd’hui à l’œuvre dans les processeurs à cœur Cortex-R, et destinée à étoffer l’architecture ARMv8-A, l’architecture ARMv8-R se distingue essentiellement par l’intégration dans le silicium d’un mode hyperviseur. Un mode qui permet l’exécution de plusieurs systèmes d’exploitation, applications et tâches temps réel sur un seul et unique processeur, tout en assurant une parfaite isolation entre des environnements qui n’obéissent pas forcément aux mêmes contraintes de sécurité ou de sûreté de fonctionnement.

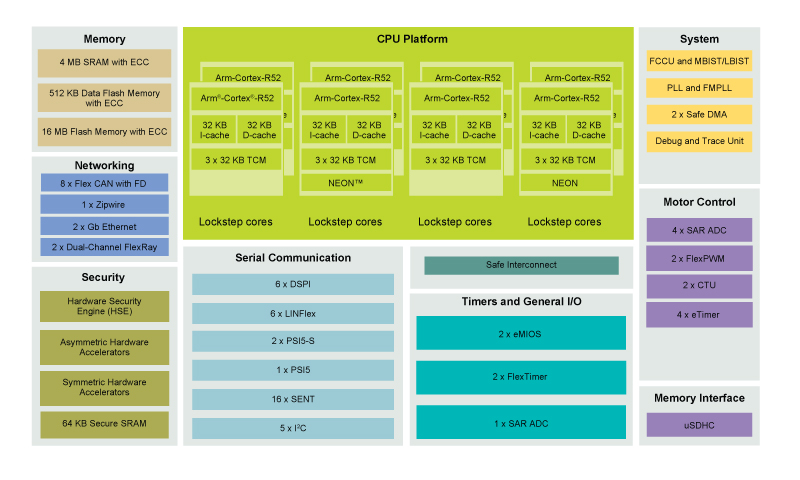

Dans le détail, le premier membre de la famille S32S (le S32S24) embarque quatre cœurs Cortex-R52 en mode lockstep (soit huit cœurs en tout) cadencés à 800 MHz. Selon NXP, cette architecture permet la mise en place de quatre voies de traitement de niveau Asil D complètement indépendantes pour assurer un parallélisme « sûr ». En outre, l’architecture dispose d’une fonction de « disponibilité en cas de faute » (fail availability) qui permet à la puce de continuer de fonctionner après détection et mise en isolement d’une erreur, une fonction critique pour les futures applications autonomes, précise NXP.

Le fabricant de semi-conducteurs a par ailleurs collaboré avec l’éditeur allemand OpenSynergy, spécialiste des solutions logicielles embarquées dans l’automobile et propriété de Panasonic depuis l’été 2016, pour élaborer un hyperviseur temps réel apte à prendre en charge les produits S32S de NXP. Le SDK Coqos Micro est l’un des premiers hyperviseurs à tirer profit des mécanismes matériels de prise en charge de la virtualisation implémentés dans le cœur Arm Cortex-R52 (lire notre article ici). Il a donc la capacité de faire tourner plusieurs systèmes d’exploitation temps réel sur des microcontrôleurs qui exigent des niveaux élevés de sûreté et de faire cohabiter sur un même microcontrôleur différents environnements logiciels issus de fournisseurs distincts.

Les processeurs S32S embarquent par ailleurs jusqu’à 64 Mo de mémoire flash (pour faciliter notamment les mises à jour over-the-air et à la volée sans arrêt de la puce), un moteur de sécurité programmable, une interface PCIe et tout un ensemble de périphériques pour la commande de moteurs électriques (avec les bibliothèques logicielles associées).