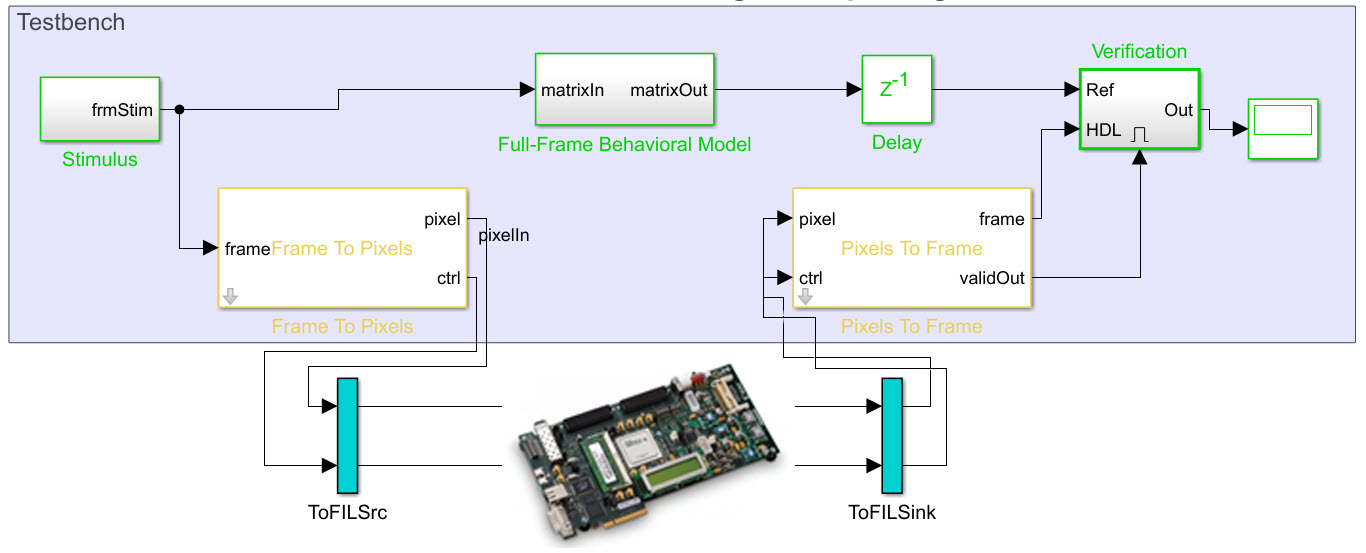

Avec son outil HDL Verifier, l’éditeur d’outils de développement, de simulation et de vérification MathWorks accélère la vitesse d’exécution de systèmes de vérification de code embarqué dits HIL (Hardware In The Loop) grâce à des cartes ...basées sur des FPGA, et ce en autorisant notamment le réglage précis et personnalisé de la fréquence de fonctionnement du FPGA utilisé. Introduite dans la version 2016B de HDL Verifier, cette possibilité de réglage fin de l’horloge du FPGA, adaptée en fonction du programme à vérifier, amène des gains de vitesse de vérification d’un facteur 4 à 5 par rapport à des systèmes classiques à fréquence fixe.

Ainsi, pour des applications qui mettent à profit les technologies d’overcloking (augmentation forcée de la fréquence d'horloge des processeurs), les utilisateurs peuvent connecter via un lien PCI Express une carte à base de FPGA et obtenir des bandes passantes élevées pour l’analyse de données avec des modèles Simulink ou des algorithmes écrits dans Matlab. Les FPGA supportés sont les modèles KC705/VC707 de Xilinx et les Cyclone V GT/Stratix V DSP d’Intel (issus du rachat d’Altera). Avec à la clé des vitesses de simulation de 3 à 4 fois supérieures à ce que l’on aurait obtenu, selon MathWorks, avec un lien Gigabit Ethernet.

« Face à la complexité accrue des systèmes électroniques, le besoin de précision dans les phases de vérification du code sur des prototypes est très important, explique Jack Erickson, product manager chez MathWorks. L’augmentation des vitesses d’horloge sur des systèmes HIL, proches de celles qui seront mises en œuvre sur les cibles matérielles définitives, va dans ce sens. »