Après les sociétés Cadence et Ceva, c’est au tour de Synopsys d’annoncer la prise en charge du framework TensorFlow Lite for Microcontrollers de Google. La société américaine l’a optimisé pour ses cœurs de processeur dopés aux fonctions DSP DesignWare ARC EM et ARC HS. ...

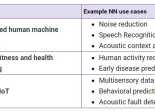

TensorFlow Lite for Microcontrollers a été conçu pour déployer des modèles compacts d’apprentissage automatique (machine learning, ML) sur des processeurs éco-efficaces implantés dans des produits de périphérie de réseau (edge). Comme son nom l’indique, il s’agit d’un portage de TensorFlow Lite élaboré pour exécuter des modèles ML sur des microcontrôleurs ou d’autres circuits dotés de quelques kilooctets de mémoire seulement. Cet environnement ne nécessiterait pas de système d’exploitation, de bibliothèques C ou C++ standard ou d’allocation mémoire dynamique. Son runtime tiendrait dans 16 Ko sur un Arm Cortex-M3 et un modèle de détection vocale de mots clés pourrait se satisfaire d’une capacité mémoire de seulement 22 Ko.

« TensorFlow Lite for Microcontrollers permet aux développeurs de générer rapidement des modèles d'apprentissage automatique pour un déploiement simplifié de réseaux de neurones sur des équipements de faible consommation, assure Pete Warden, responsable technique chez Google. L'implémentation optimisée du logiciel sur les processeurs ARC de Synopsys va permettre aux utilisateurs de développer efficacement la reconnaissance vocale par mots clés, la classification de gestes et d'autres applications reposant sur l'apprentissage automatique sur des dispositifs aux ressources limitées. »

Le portage du framework sur les processeurs ARC s’appuie sur la bibliothèque logicielle embARC Machine Learning Inference (MLI), qui prend en charge tous les processeurs ARC EM et HS renforcés par des fonctions DSP, notamment les références ARC EM5D, EM7D, EM9D et EM11D à ultrabasse consommation et les processeurs ARC HS45D et HS47D à hautes performances. Selon Synopsys, la bibliothèque MLI fournit un ensemble de noyaux essentiels pour l’inférence efficace des modèles d'apprentissage automatique de taille petite ou moyenne, avec à la clé des performances cinq fois supérieures à celles atteintes avec les noyaux de référence TensorFlow Lite for Microcontrollers.

La version TensorFlow Lite for Microcontrollers optimisée pour les processeurs DesignWare ARC EM avec fonctions DSP est déjà disponible dans le référentiel du framework sur GitHub. Celle pour les processeurs ARC HS le sera au troisième trimestre.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’intelligence artificielle dans l’embarqué : Embedded-IA