[EMBEDDED WORLD] Conçu pour l’analyse et le débogage des puces-systèmes SoC haut de gamme, la version 5.0 de l’environnement Universal Debug Engine (UDE) de l’éditeur allemand PLS (Programmierbare Logik & Systeme) s’attaque dorénavant au délicat problème de l’étude des applications virtualisées, ...en particulier celles déployées sur les architectures Arm Cortex-A53 qui utilisent l'hyperviseur LynxSecure de Lynx Software Technologies. Alors qu’il existe actuellement une tendance forte à la consolidation, sur une même plate-forme de traitement, de plusieurs applications qui auparavant utilisaient du matériel séparé, les exigences qui en découlent en termes de sécurité et de sûreté de fonctionnement nécessitent des technologies d’isolation stricte, qui ne peuvent être atteintes que par la virtualisation.

Grâce à la prise en compte de ces technologies d’hypervision par l’environnement UDE, les développeurs peuvent désormais utiliser les fonctionnalités de débogage classiques pour mettre au point des applications virtualisées. Concrètement, les fonctionnalités spécifiques de l’architecture Arm Cortex-A53 par exemple, telles que la traduction d'adresses en deux étapes (two-stage address translation) ou la prise en charge des interruptions virtuelles, sont gérées de manière transparente pour l’utilisateur. Cette prise en compte de l'hyperviseur par l’outil UDE autorise ainsi le développeur à déboguer une application, sans connaissance du système d'exploitation comme à son habitude, comme si elle fonctionnait directement sur du matériel au lieu d'être encapsulée au sein d’une machine virtuelle.

Si nécessaire, l’outil UDE prend également en charge le débogage et l'analyse système de l'hyperviseur lui-même. Pour chaque machine virtuelle individuelle, l'état et les contextes peuvent être affichés. De plus, le logiciel fournit des informations sur la disposition de la mémoire des machines virtuelles individuelles ainsi que sur le “mappage” des adresses de mémoire virtuelle sur les adresses de mémoire physique.

Si nécessaire, l’outil UDE prend également en charge le débogage et l'analyse système de l'hyperviseur lui-même. Pour chaque machine virtuelle individuelle, l'état et les contextes peuvent être affichés. De plus, le logiciel fournit des informations sur la disposition de la mémoire des machines virtuelles individuelles ainsi que sur le “mappage” des adresses de mémoire virtuelle sur les adresses de mémoire physique.

Au-delà, dans cette version 5.0 d’UDE, le traitement de grandes quantités de données de trace enregistrées a été simplifié, avec une attention particulière portée sur la visualisation des résultats d’analyse. Par exemple, les fonctions exécutées et les tâches du système d’exploitation affichées dans le tableau de séquence d’exécution peuvent dorénavant être triées et filtrées en fonction de différents critères avec un lien permettent une navigation sur les fonctions enregistrées et l’accès au code source correspondant.

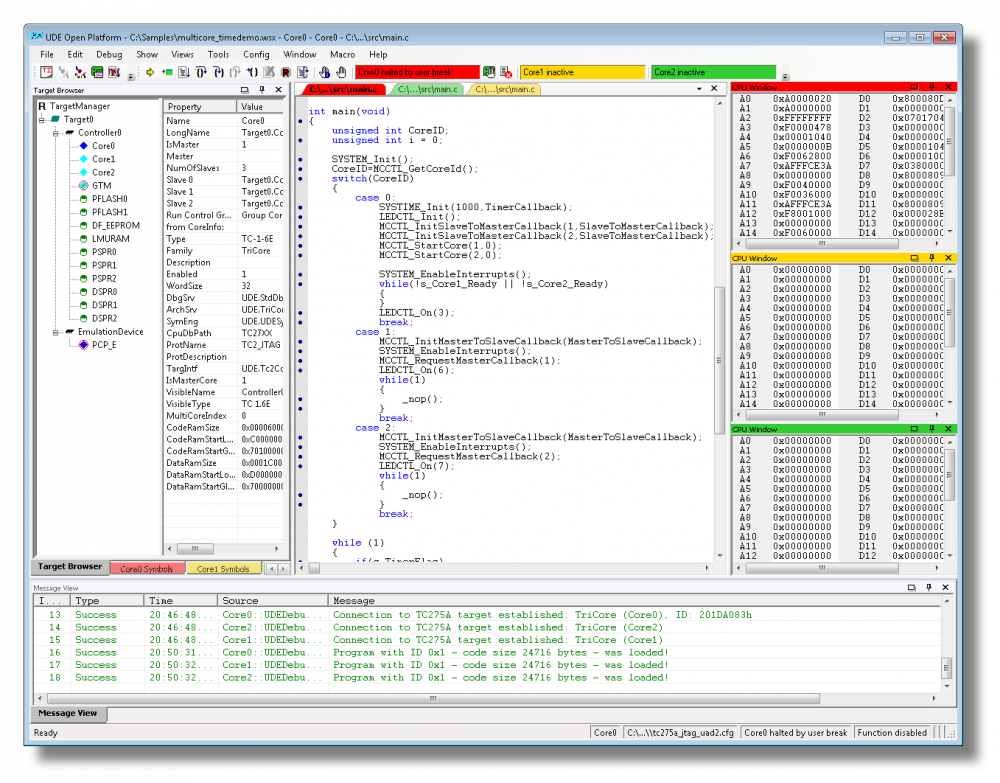

En tant que débogueur multicœur, l’UDE 5.0 prend également en charge la visualisation des états et le contrôle de tous les cœurs d'un système multicœur au sein d'une interface unique. Les traitements des variables que le compilateur a rendu visibles pour un noyau spécifique sont affichés dans des fenêtres dites de “surveillance” au sein desquelles les variables locales des noyaux sont séparées par des couleurs différentes en fonction de leur noyau respectif.

Au niveau des microcontrôleurs, PLS met en avant le support des architectures 64 bits, comme l'Arm Cortex-A53. Les architectures de dernière génération comme l’Arm Cortex-R52 à 32 bits et le microcontrôleur de communication netX 90 de Hilsher fondé sur des Cortex-M ont été ajoutées, au même titre que le Chorus SPC58NH92x à architecture Power de STMicroelectronics et les microcontrôleurs MPC5775B/MPC5775E de NXP, eux aussi à architecture Power (cœurs e200z7). Parallèlement les microcontrôleurs de la famille TC3xxx d’Infineon bénéficient des fonctions étendues de débogage avec une une prise en charge de la trace disponible. Enfin, un adaptateur pour les architecture Aurix est disponible pour la communication entre la cible et l’environnement UDE (Universal Access Device 3+).