NXP compte échantillonner au cours du premier trimestre 2025 les premiers membres de la famille i.MX 94, dernière en date de la gamme de processeurs d’application i.MX 9 qui compte déjà à son actif les références i.MX 91, i.MX 93 et i.MX 95.

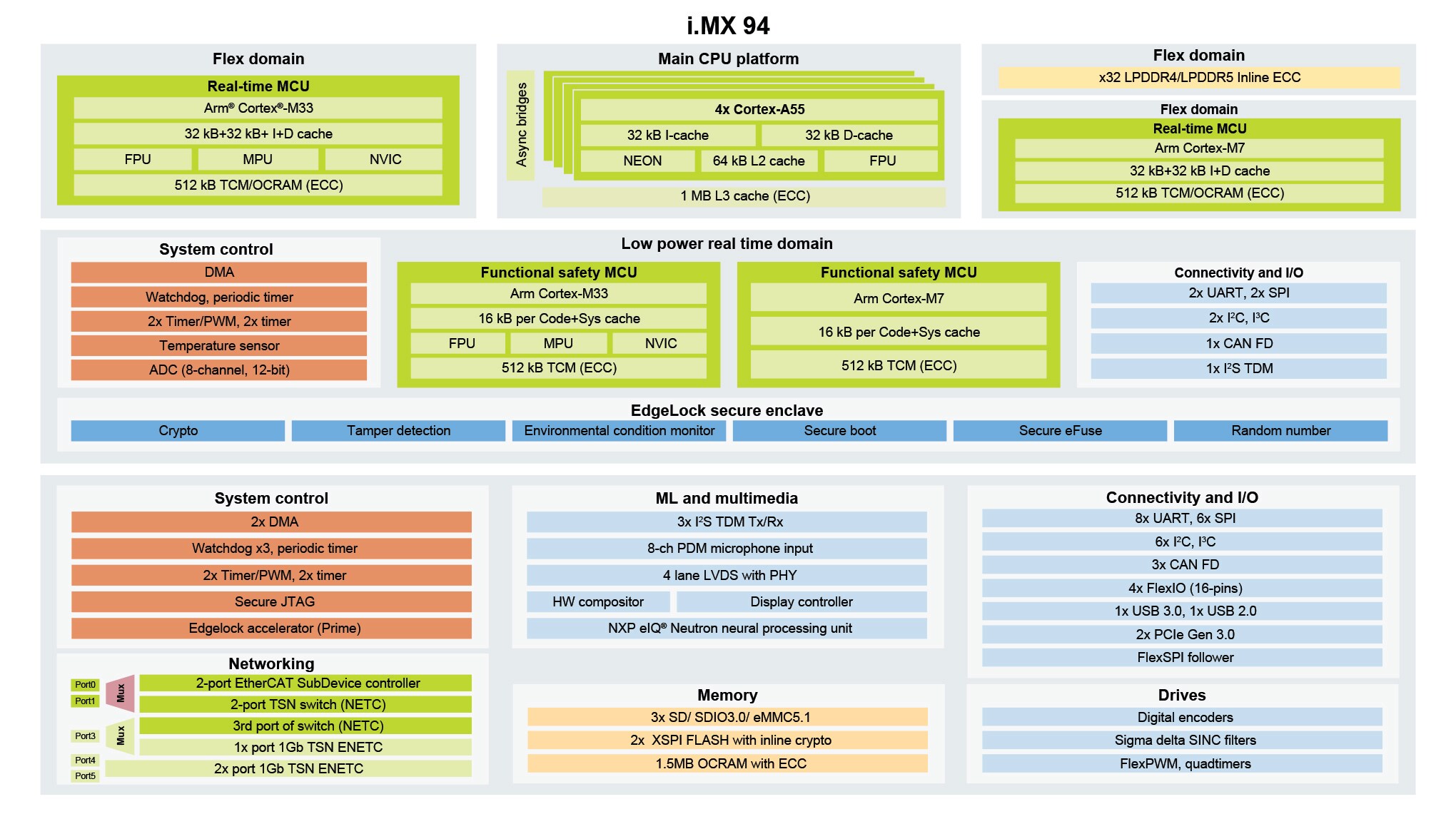

Conçus pour les besoins des systèmes de commande industriels, des automates programmables, des produits télématiques, des passerelles industrielles et automobiles et des applications de contrôle des bâtiments et de l’énergie, les puces-systèmes multicœurs 64 bits i.MX 94 intègrent jusqu'à quatre cœurs Arm Cortex-A55 (où peut s’exécuter un environnement Linux), ainsi que deux cœurs Cortex-M33 et deux cœurs Cortex-M7 pour offrir une capacité de traitement temps réel accrue.

L’ensemble est pris en charge par le framework logiciel Real-Time Edge de NXP qui permet aux développeurs de combiner de façon optimale des tâches temps réel et applicatives s’exécutant sur l'un quelconque de ces cœurs. Les i.MX 94 peuvent également faire tourner des systèmes d'exploitation temps réel tiers (QNX Neutrino, Green Hills Integrity…) et dispose aussi d'un îlot à sécurité fonctionnelle intégré et d'une partition à sûreté de fonctionnement configurable afin d’assurer la conformité aux normes CEI 61508 (au niveau SIL2) et ISO 26262 (au niveau Asil-B).

Afin de satisfaire les contraintes d’environnements industriels de plus en plus complexes sui s'appuient sur une grande variété de protocoles de communication, la famille i.MX 94 inclut ce que NXP qualifie de premier processeur d'application i.MX à intégrer un commutateur Ethernet 2,5 Gbit/s compatible TSN (Time Sensitive Networking), avec une initialisation rapide et une prise en charge des modes basse consommation. Ici le logiciel Real-Time Edge de NXP se fait fort d’assurer le support d’une grande variété de protocoles industriels, des implémentations « historiques » jusqu’aux derniers développements en date tels qu’OPC-UA FX et OPC-UA PubSub.

Dans le détail, la famille i.MX 94 prend en charge les protocoles de bus de terrain série traditionnels tels que Profibus, Modbus, CANopen et IO-Link, les protocoles réseau temps réel reposant sur Ethernet comme Profinet, EtherCAT, Ethernet/IP, CC-Link, etc. ainsi que les implémentations TSN de ces protocoles (AVB/TSN, Ethernet OPC-UA, Profinet over TSN…).

Côté sécurité, NXP précise que les puces i.MX 94 sont les premiers processeurs d'application de la société à offrir une cryptographie à clé publique post-quantique, ce qui leur permet de résister aux attaques des ordinateurs quantiques et de gérer la sécurité des équipements sur un long cycle de vie. Ici, l'enclave sécurisée EdgeLock (Advanced Profile) intégrée permet de restaurer la puce à un état de confiance à tout moment, tout en offrant des capacités de sécurité avancées (au niveau du démarrage, du débogage et des mises à jour sécurisée du processeur) reposant sur la cryptographie post-quantique sans compromettre les performances.

Enfin, pour le cas particulier des applications industrielles TSN et de connectivité automobile, l'i.MX 94 intègre un accélérateur cryptographique (Edge Accelerator Prime) permettant un démarrage rapide, ainsi que la signature, l'authentification et le chiffrement de messages à grande vitesse et en temps réel à des débits 5G pour des communications sécurisées.

Au final, assure NXP, la famille i.MX 94 s’aligne sur les normes de sécurité telles que CEI 62443 et ISO 21434, ainsi que sur les réglementations à venir telles que le Cyber Resilience Act en Europe.

A noter qu’à l’instar des i.MX 93, les i.MX 94 intègrent l’unité de traitement neuronal (NPU) maison de NXP estampillée eIQ Neutron et affichant des performances d'apprentissage automatique de 0,5 Tops. De quoi assurer des applications telles que la maintenance prédictive et le guidage d’un opérateur en temps réel, ainsi que l'analyse des défauts et le diagnostic des machines. Selon NXP, le NPU est aussi capable de fournir une détection et une protection contre les intrusions avec une cybersécurité assistée par apprentissage automatique afin de protéger systèmes et infrastructures critiques contre toute manipulation future.

-dissolve-basic-fr.jpg)