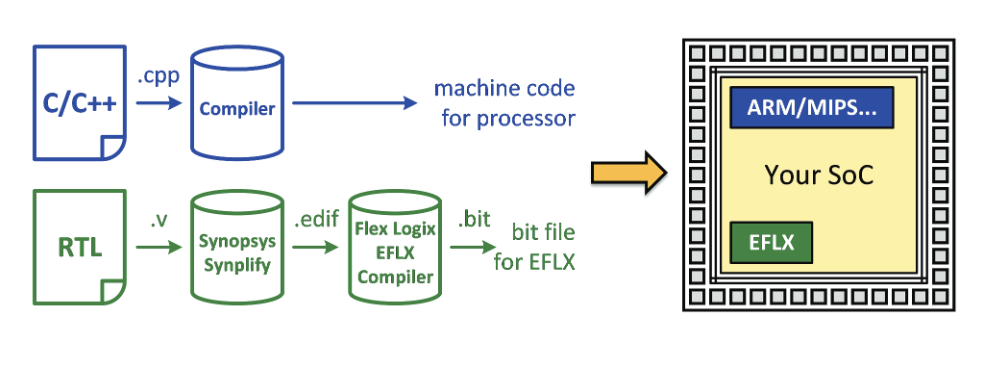

Fournisseur d’une technologie dite eFPGA (embedded FPGA) délivrée sous la forme d’un bloc d’IP intégrable au sein de puces-systèmes et de circuits Asic, la société californienne Flex Logix annonce la disponibilité, en version alpha, de l'environnement de compilation eXpreso. Ce compilateur de nouvelle génération procure, selon la société, une fréquence jusqu'à 1,5 fois plus élevée, un conditionnement des tables LUT (Look Up Table) deux fois plus dense et des temps de compilation dix fois plus rapides pour toutes les “tuiles” (tiles) et les portes (gates).

L’objectif de cet outil, en développement depuis plusieurs années chez le Californien, est de délivrer une flexibilité et des performances jugés cruciales pour faciliter chez les concepteurs de puces-systèmes et d’Asic une adaptabilité vis-à-vis des normes, protocoles, et autres algorithmes de cryptographie post-quantique embarqués qui sont toujours en perpétuelle évolution.

Selon Flex Logix, cet outil de compilation autorise également une gestion optimisée des blocs d'accélération logicielle et le traitement déterministe des données. Toujours selon l'entreprise, eXpreso améliore ainsi la valeur de l'eFPGA en minimisant la surface silicium de la puce, ce qui permet de réduire coût et consommation.

« Avec l’outil eXpreso, le design d’un bloc de cryptographie AES256 est "compressé" sous forme de 2 tuiles alors qu’il en fallait 6 auparavant, explique Cheng Wang, le CTO de Flex Logix. Un algorithme de cryptographie atteint désormais 98,6% d'utilisation de tables LUT – ce qui n'était pas réalisable auparavant, même avec les outils de Xilinx. »

-dissolve-basic-fr.jpg)