Alors que la prochaine édition du RISC-V Summit se profile à l’horizon (la manifestation se tient les 7 et 8 novembre à Santa Clara en Californie), la société Codasip, spécialiste des cœurs de processeur embarqués RISC-V destinés aux concepteurs de puces-systèmes, dévoile sous le label générique de "700" une famille de processeurs hautement configurables qui se déclinera à la fois en cœurs d’application et en cœurs embarqués.

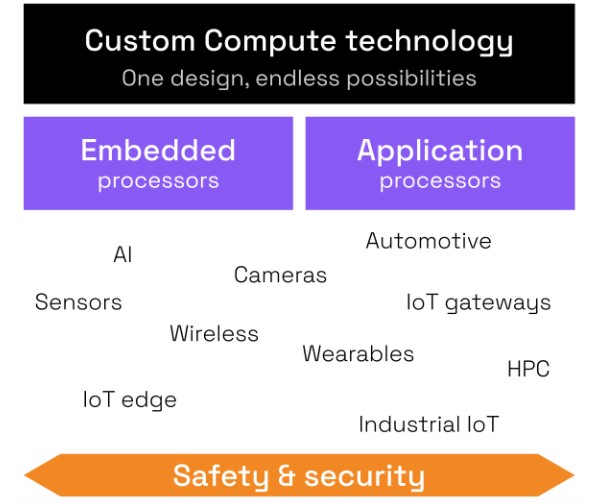

Selon Codasip, cette nouvelle famille se distingue des cœurs embarqués déjà proposés par la firme allemande (d’origine tchèque) par sa capacité à proposer différentes approches aux utilisateurs pour atteindre le niveau d’optimisation qu’ils recherchent (et, partant, de meilleures performances). « Avec la famille 700 et l’approche Codasip Custom Compute, les concepteurs peuvent repousser les limites technologiques en apportant des optimisations au niveau de la puce ou au niveau de l'application afin d’obtenir des gains inédits tout en gardant les coûts sous contrôle », précise Filip Benna, directeur produits chez Codasip.

Selon Codasip, cette nouvelle famille se distingue des cœurs embarqués déjà proposés par la firme allemande (d’origine tchèque) par sa capacité à proposer différentes approches aux utilisateurs pour atteindre le niveau d’optimisation qu’ils recherchent (et, partant, de meilleures performances). « Avec la famille 700 et l’approche Codasip Custom Compute, les concepteurs peuvent repousser les limites technologiques en apportant des optimisations au niveau de la puce ou au niveau de l'application afin d’obtenir des gains inédits tout en gardant les coûts sous contrôle », précise Filip Benna, directeur produits chez Codasip.

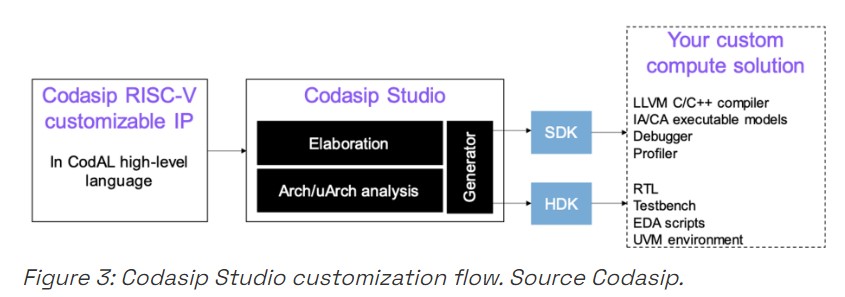

Dans la pratique, ces optimisations peuvent être effectuées pour chaque cas d’usage par le biais de l’outil de conception automatisé Codasip Studio au niveau architectural et à travers une analyse des performances au niveau applicatif. En automatisant la conception du processeur (à partir d’une IP en langage de haut niveau CodAL) et la génération d'un SDK (Software Development Kit) et d'un HDK (Hardware Development Kit) personnalisés, les ingénieurs peuvent obtenir de meilleurs résultats et de manière plus efficace, assure la société.

L'automatisation accélère également l'exploration, l'investigation et la configuration pour maximiser toute optimisation. Ainsi, en profilant le logiciel et en examinant les goulots d'étranglement, il serait possible d'explorer l'architecture de la famille 700 et de définir les domaines dans lesquels les modifications de conception ont du sens. Avec Codasip Studio, les équipes logicielles et matérielles peuvent par ailleurs collaborer pour améliorer l’efficacité système. En effectuant un profilage dans l’environnement de conception de Codasip, les différentes équipes seraient ainsi en mesure d’effectuer l'analyse et de suggérer des modifications à l'équipe en charge du hardware.

Dans la pratique, les cœurs de la famille 700 pourront toutefois être utilisés aussi tels quels dans des configurations standard prêtes à l’emploi (en code RTL) pour un démarrage immédiat.

A noter enfin que le premier membre de la famille, estampillé A730 et présenté comme un cœur d’application RISC-V 64 bits de milieu de gamme, est déjà proposé à des utilisateurs privilégiés. Apte à exécuter deux instructions par cycle (dual-issue), il est disponible dans des configurations mono et multicœurs et dispose d’options de configuration qui le rendraient deux fois plus performant que les générations précédentes.

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’architecture de processeur RISC-V : Embedded-RISCV

-dissolve-basic-fr.jpg)