Synopsys annonce la disponibilité de la bibliothèque logicielle embARC MLI (Machine Learning Inference) dont la vocation est de faciliter le développement de puces-systèmes éco-efficaces bâties sur ses cœurs de processeurs DSP DesignWare ARC EM et HS et optimisées pour l’exécution de réseaux de neurones. ...

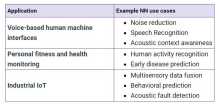

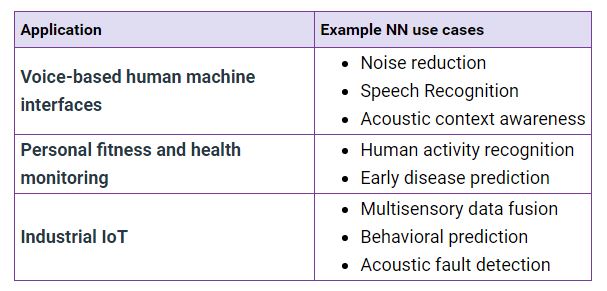

Open source et disponible gratuitement sur le site embARC.org, la bibliothèque fournit aux développeurs les fonctions nécessaires à l’implémentation des couches de réseaux de neurones convolutifs (CNN) ou récurrents (RNN) pour les applications qui exigent à la fois une faible consommation et une faible empreinte silicium comme la détection vocale, la reconnaissance de la parole ou le traitement de données issues de capteurs. Utilisable sur les processeurs ARC EMxD et HS4xD, elle fournit un jeu de noyaux essentiels pour l’inférence de modèles d’apprentissage automatique de taille modérée à faible, et assure une implémentation éco-efficace d’opérations telles que les convolutions, les cellules LSTP (Long Short Term Memory), le « pooling », les fonctions d’activation (comme l’unité de rectification linéaire ReLU) et les opérations de routage de données (padding, concaténation, transposition…).

« La consommation électrique et l’empreinte silicium sont deux critères critiques à considérer lorsqu’on embarque des fonctions d’apprentissage automatique dans des équipements de périphérie de réseau (edge), indique John Koeter, vice-président marketing en charge des IP chez Synopsys. En permettant à différentes catégories de réseaux de neurones de s’exécuter sur nos processeurs DSP à faible consommation ARC EM et HS, Synopsys étend la gamme de processeurs ARC que les développeurs peuvent sélectionner pour leurs conception IA éco-efficaces. »

Vous pouvez aussi suivre nos actualités sur la vitrine LinkedIN de L'Embarqué consacrée à l’intelligence artificielle dans l’embarqué : Embedded-IA