L’architecture open source de processeur RISC-V reçoit aujourd’hui un soutien de poids. Le fournisseur de semi-conducteurs Microsemi est le premier spécialiste des FPGA à proposer une IP de cœur de processeur RISC-V ...et une chaîne d’outils logiciels ad hoc. Accessible sous licence open source BSD et sans paiement de redevances à la différence des approches "commerciales" de sociétés comme ARM ou Imagination Technologies (propriétaire de Mips), RISC-V, rappelons-le, définit un jeu d’instructions basé sur les principes des architectures matérielles de processeurs Risc (Reduced Instruction Set Computer). Selon ses promoteurs, ses caractéristiques, doublées de ses capacités d’extension (avec des instructions d’unité de calcul en virgule flottante par exemple), le rendent adapté aussi bien aux serveurs dans le cloud qu’aux terminaux mobiles ou aux systèmes embarqués les plus contraints. (Pour plus de détails, lire notre article Une alternative open source commence à briller au firmament des architectures de processeurs.)

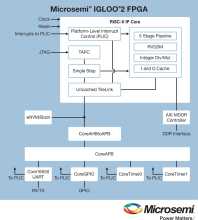

Développé avec la collaboration de la jeune société SiFive, fondée par les créateurs de l’architecture RISC-V à l’université de Californie à Berkeley (Krste Asanovic, Yunsup Lee et Andrew Waterman), le cœur RISC-V RV32IM de Microsemi est d’ores et déjà disponible pour les FPGA Igloo2 et RTG4 ainsi que pour les SoC programmables SmartFusion2 de l’Américain. Il est accompagné d’un environnement de développement intégré (IDE) Eclipse SoftConsole pour hôte Linux et de la suite de conception de SoC Libero.

Développé avec la collaboration de la jeune société SiFive, fondée par les créateurs de l’architecture RISC-V à l’université de Californie à Berkeley (Krste Asanovic, Yunsup Lee et Andrew Waterman), le cœur RISC-V RV32IM de Microsemi est d’ores et déjà disponible pour les FPGA Igloo2 et RTG4 ainsi que pour les SoC programmables SmartFusion2 de l’Américain. Il est accompagné d’un environnement de développement intégré (IDE) Eclipse SoftConsole pour hôte Linux et de la suite de conception de SoC Libero.

Selon Microsemi, très impliqué au sein de la Fondation RISC-V, créée en 2015 et portée par des poids lourds comme Google, Hewlett Packard Enterprise (HPE), IBM, Microsoft, Oracle ou Western Digital, le cœur RV32IM est particulièrement adapté aux applications aux fortes contraintes en termes de sécurité et de sûreté de fonctionnement, le code source RTL étant accessible à des fins d’inspection. Du coup les utilisateurs peuvent vérifier eux-mêmes le niveau de sécurité du processeur, ce qui n’est pas possible avec les architectures propriétaires, et associer plusieurs cœurs RISC-V afin d’assurer un certain niveau de redondance pour les applications critiques. « Nos composants Igloo2, SmartFusion2 et RTG4 sont des FPGA idéalement adaptés au cœur RISC-V en raison de leur faible consommation énergétique et de leur capacité à protéger et sécuriser l’IP des utilisateurs dans les domaines de l’industriel, de la Défense, de la sécurité et du médical », a commenté Venki Narayanan, directeur senior en charge de l’ingénierie logicielle et système pour l’activité Produits SoC de Microsemi.