[EMBEDDED WORLD 2017] La jeune société belge Hipperos, basée à Louvain et cofondée en 2014 par Joël Goossens, chercheur à l’université libre de Bruxelles (ULB), est l’éditeur et le promoteur d’un système d’exploitation... temps réel original, destiné aux applications embarquées exigeantes en termes de puissance de traitement mais contraintes en termes de consommation électrique. Issu des travaux de l’ULB, l’OS temps réel d’Hipperos est taillé pour ce type de systèmes grâce à une conception prévue nativement pour le traitement en parallèle des processus, au support des technologies d’accélération matérielles, à la gestion optimisée des mécanismes IPC (Inter Process Communication) entre cœurs d’un même processeur, et à un ordonnanceur (scheduler) adapté à la gestion de toutes ces caractéristiques.

Configurable par l’utilisateur, Hipperos (pour High Performance Parallel Embedded Real Time Operating System) est échelonnable au niveau de son noyau basé sur une architecture maître/esclave novatrice dans laquelle le maître gère les données du noyau, l’ordonnanceur et le partage des tâches, alors que l’esclave exécute les tâches sur chaque cœur de processeur, minimisant de ce fait les commutations de contexte (context switches), les overheads et les verrouillages au niveau du noyau (kernel locks). Cette architecture est capable en outre de coordonner des tâches logicielles et matérielles de manière sécurisée grâce à une isolation spatiale et temporelle des processus du noyau en utilisant les mécanismes de MMU (Memory Management Unit) et MPU (Memory Protection Unit) présents sur le processeur utilisé.

Une approche qui fait de cet OS une brique logicielle particulièrement adaptée aux applications de traitement intensif d’images dans des contextes embarqués contraints, en particulier dans des drones, des systèmes d'imagerie médicale, dans les automobiles pour des systèmes d’aide à la conduite… Ces applications sont en effet souvent basées sur la mise en œuvre de blocs d’accélération matériels au sein d'un FPGA pour obtenir une fréquence élevée d’acquisition de trames vidéo. Ce qui nécessite un ordonnancement mixte des tâches d’un programme qui s'effectuent sur plusieurs cœurs de processeurs, tant au niveau logiciel quet matériel, et ce avec des niveaux de criticité différents. Avec en sus la nécessité de tenir compte des communications IPC très rapides entre ces cœurs via un mécanisme dit de passage de messages.

Avec Hipperos, il est possible, selon ses concepteurs, de réaliser sur ce type d’architecture des acquisitions vidéo à une fréquence de 90 images par seconde, soit à des vitesses de 10 à 20 fois plus rapides que celles mesurées sur un processeur traditionnel avec un OS temps réel classique. Autre atout, selon Hipperos, ce système d’exploitation adapté au traitement parallèle de processus multithreads permet de réduire le poids et la consommation d’un système embarqué dédié au traitement d’image par sa capacité à traiter à lui seul des tâches parallèles s'exécutant sur plusieurs cœurs.

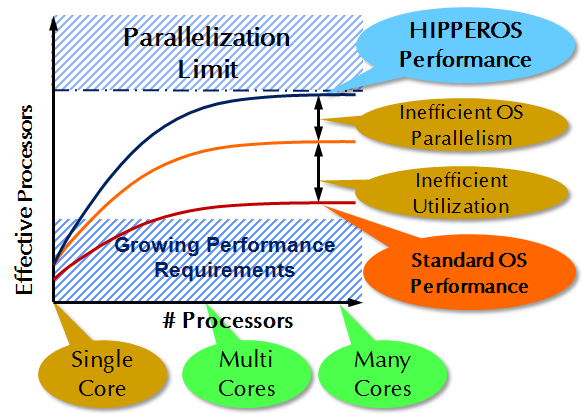

« La plupart des OS temps réel du marché n’ont pas été nativement conçus pour s’adapter aux architectures multicœurs, explique Ben Rodriguez, le CEO, CTO et cofondateur d’Hipperos. Par voie de conséquence, ils ne s’adaptent pas bien aux contraintes inhérentes au fonctionnement de ces architectures alors que la tendance pour les applications embarquées est de trouver le meilleur compris entre sécurité, performances et utilisation optimale des ressources de calcul. »

Côté métriques, Hipperos affiche une empreinte mémoire de l’ordre de 20 Ko et des temps de latence pour les commutations de contexte inférieurs à 5 microsecondes.

Encore peu connu, Hipperos profite du salon Embedded World 2017 pour montrer les capacités de sa technologie dans une application basse consommation de traitement d’image sur un SoC Zynq UltraScale 7000 de Xilinx doté d’un moteur d’accélération matérielle et implanté sur une carte de Sundance, avec en parallèle la gestion d’un chiffrement symétrique standard (AES).