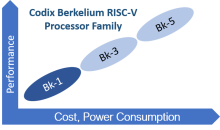

Positionnée sur le marché des cœurs de processeurs embarqués RISC-V destinés aux concepteurs de circuits intégrés de type SoC, la société tchèque Codasip vient d’ajouter un nouveau membre à sa famille Bk (pour Berkelium) qui cible plus particulièrement les objets connectés à ultrabasse consommation. ... De type machine à états finis (FSM), le processeur 32 bits Bk-1 est présenté par son concepteur comme particulièrement éco-efficace et meilleur marché que les processeurs embarqués comparables.

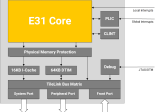

Dans sa configuration minimale, il ne comporte que 9K portes tout en affichant une fréquence maximale de 350 MHz une fois gravé en technologie 55 nm. Le cœur de processeur Bk-1 dispose en outre d’une unité de gestion de l’alimentation en option, d’un contrôleur de débogage JTAG et de ponts vers des bus Amba pour une intégration aisée dans des conceptions ARM existantes.

« Le Bk-1 est un choix idéal pour les concepteurs d’Asic IoT qui souhaitent migrer d’un processeur 8 bits vers une architecture 32 bits, précise Karel Masarik, CEO et fondateur de Codasip. Comme tous les membres de la famille Bk, notre dernier-né est totalement compatible avec le standard ouvert RISC-V. Les utilisateurs sont donc assurés de la portabilité de leurs logiciels embarqués et leurs conceptions ne sont pas verrouillées autour d’un jeu d’instructions propriétaire comme celui d’ARM. » La société fournit aussi des outils de conception de haut niveau qui permettent aux concepteurs d’Asic de calibrer le processeur Bk-1 selon les exigences de l’application ciblée.

« C’est encore une nouvelle étape essentielle pour l’écosystème RISC-V qui démontre la montée en puissance de cette architecture ouverte et gratuite sur le marché », ajoute Rick O’Connor, directeur exécutif de la fondation RISC-V, dont Codasip, société créée en 2006, est un membre fondateur. (Lire aussi notre article L’architecture de processeurs open source RISC-V fait son show sur Embedded World.)

Le cœur de processeur Bk-1 est vendu sous licence à partir de 40 000 dollars, un prix compétitif par rapport à ceux des processeurs accessibles au travers du programme ARM DesignStart, précise Codasip. Il est par ailleurs disponible sans paiement de royalties, ce qui permettrait aux concepteurs d’Asic d’économiser au moins 300 000 à 400 000 dollars en coûts supplémentaires par rapport aux cœurs ARM et autres alternatives du marché (Andes, Cortus, etc.), ajoute encore la société tchèque.